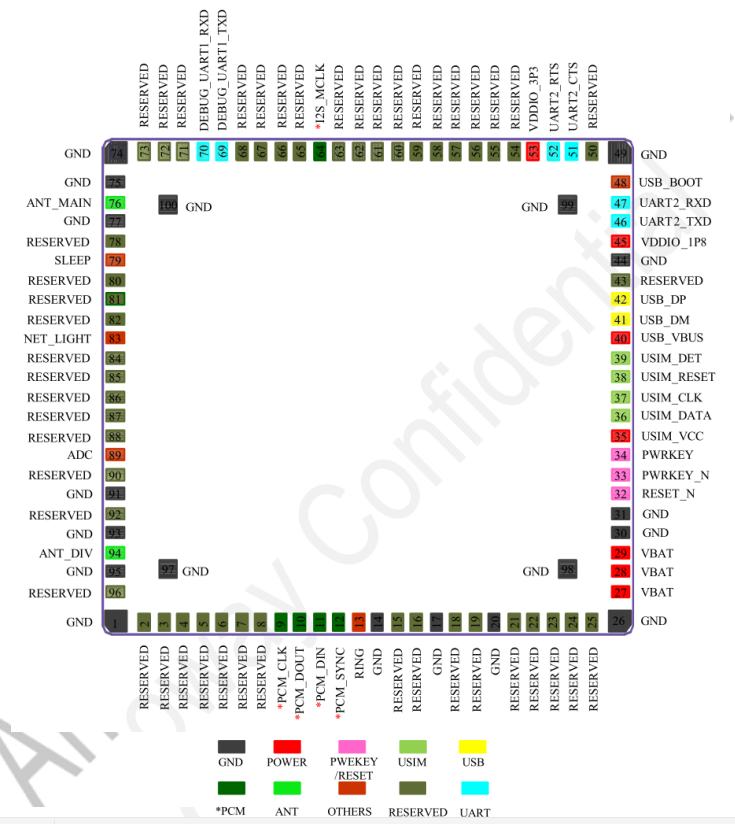

管脚说明

## 1. 管脚定义图

## 2. 管脚定义说明

|IO|类型说明|

|-|-

|B|数字输入输出,COMS 逻辑电平|

|DO|数字输出,COMS 逻辑电平|

|DI|数字输入,COMS 逻辑电平|

|PO|电源输出|

|PI|电源输入|

|AO|模拟输出|

|AI|模拟输入|

|AIO|模拟输入输出|

|类型|直流特性说明|-|-|

|-|-|-|-|

|P1|双电压 USIM 接口电压类型, 1.8V 或 3.0V|1.8V 直流特性 VIH=1.26~2.1V VIL=0.3~0.54V VOH=1.44~1.8V VOL=0~0.36V|3.0V 直流特性 VIH=2~3.3V VIL=-0.3~0.57V VOH=2.4~3.0V VOL=0~0.6V|

|P3|1.8V 数字 IO 电压类型|VIH =1.26~2.1V, VOH =1.44~1.8V,|VIL = -0.3~0.54V , VOL=0~0.36V|

Pin|引脚|描述|I/O|电平说明|备注|

|-|-|-|-|-|-|-|

|**电源**

|27,28,29|VBAT|直流电源供应|I|3.3V~4.3V,推荐3.8V|外部电源最大需要提供 2A 电流|3.3V~4.3V,推荐3.8V|

|1、14、17、20、26、30、31、44、49、74、75、77、91、93、95、97、98、99、100|GND|接地|-|-|请保证所有 GND 引脚都接地|

|**控制&状态**

|33|PWRKEY_N|模块开机控制|DI|VIH max=VBAT-0.3V,VIL =0~1.8V|高电平触发有效,可控制模块开机,不使用则悬空|

|34|PWRKEY|模块开机控制|DI|VIH min=1.1V,VIH norm=1.8V,VIH max=VBAT-0.3V|低脉冲触发有效,可控制模块开机,不使用则悬空;由于管脚上拉到 VBAT,所以默认 输 出 电 平 等 于VBAT|

|45|VDDIO_1P8|LDO 输出信号,显示模块的开机|PO|Vnorm=1.8V; Imax=50mA|仅用于电平转换,不使用则悬空|

|53|VDDIO_3P3|LDO 输出信号,显示模块的机|PO|Vnorm=3.3V;Imax=100mA|仅用于电平转换,不使用则悬空|

|32|RESET_N|模块复位输入|DI|VIH max=VBAT-0.3V,VIL =0~1.8V|低脉冲触发有效,可控制模块复位,不使用则悬空,由于管脚上拉到 VBAT,所以默认 输 出 电 平 等 于VBAT|

|79|SLEEP|休眠模式控制|DI||低电平触发有效,可控制模块休眠,不使用则悬空。|

|13|RING|开机/来电信息指示灯控制|DO|-|不使用则悬空。|

|83|NET_LIGHT|网络指示灯控制|DO|-|不使用则悬空。|

|47|UART2_RXD|模块接收数据|DI|P3|用于数据传输|

|46|UART2_TXD|模块发送数据|DO|P3|用于数据传输|

|52|UART2_RTS|请求发送|DO|P3|不使用则悬空|

|51|UART2_CTS|清空发送|DI|P3|不使用则悬空|

|**TRACE**

|69|DEBUG_UART1_TXD|发送数据|DO|P3|仅用于获取模块 log,不使用则悬空。|

|70|DEBUG_UART1_RXD|接收数据|DI|P3|仅用于获取模块 log, 不使用则悬空。

|**USIM 接口**

|35|USIM_VCC|电压检测管脚|PO|1.8V USIM:Vmin=1.2V Vmax=1.9V 3.0V USIM:Vmin=2.5V Vmax=3.0VIOmax =50mA|模块自动选择1.8V 或者 3.0V|

|36|USIM_DATA|USIM 数据输入、输出|DIO|-|需要上拉 10K 电阻USIM_VCC|

|37|USIM_CLK|UUSIM 时钟输出|DO|P1|-|-|

|38|USIM_RESET|USIM 复位|DO|P1|-|-|

|39|USIM_DET|USIM 检测|DI|P3|-|-|

|**USB接口**

|40|USB_VBUS|电压检测管脚|PI|Vmin=3.3V,Vmax=5.2V,Vnorm=5V|用于软件下载及数据传输,DM 和 DP 差分走线,阻抗控制 90Ω,不使用则悬空。|

|41|USB_DM|USB 数据负信号|AIO|符合 USB2.0 标 准规格|用于软件下载及数据传输,DM 和 DP 差分走线,阻抗控制 90Ω,不使用则悬空。|

|42|USB_DP|USB 数据正信号|AIO|符合 USB2.0 标 准规格|用于软件下载及数据传输,DM 和 DP 差分走线,阻抗控制 90Ω,不使用则悬空。|

|**ADC 接口**

|89|ADC|通用模拟转数字信号|AI|Vmax=1.4V;Vmin=0V|12-bit,可检测电范围:0~1.4V,不使用则悬空。|

|**PCM接口**|PCM 功能正在开发中,暂不对外开放

|12|*PCM_SYNC|PCM 同步信号|B|P3|可复用I2S_WS,不使用则悬空|

|9|*PCM_CLK|PCM 数据时钟|DO|P3|可复用I2S_SCLK, 不使用则悬空|

|11|*PCM_DIN|PCM 数据接收|DI|P3|可复用 I2S_RX,不使用则悬空|

|10|*PCM_DOUT|PCM 数据发送|DO|P3|可复用 I2S_TX,不使用则悬空|

|64|*I2S_MCLK|I2S 主时钟|DO|P3|默认频率26MHz,不使用则悬空|

|**射频接口**

|76|ANT_MAIN|主天线管脚|-|-|走线控制 50欧姆|

|94|ANT_DIV|分集天线管脚|-|-|走线控制 50 欧姆|

|**强制下载控制接口**

|48|USB_BOOT|强制下载升级控制脚|DI|P3|直接短接到地,拉低时间不超过 5s;走线距离不得大于 30mm,ESD 保护结电容不得大于 20pF,接入 USB进入下载模式,不使用则悬空。|

|**保留**

|2、3、4、5、6、7、8、15、16、18、19、21、22、23、24、25、43、50、54、55、56、57、58、59、60、61、62、63、65、66、67、68、71、72、73、80、81、82、84、85、86、87、88、90、92、96|RESERVED|-|-|-|悬空,不允许使用和接地|